Over 4 years have passed since the first information about Exascale Heterogeneous Processor (EHP), the ambitious project of AMD to create one APU for supercomputers. This APU included not only 32 x86 Zen cores, but also a Greenland (Vega) GPU flanked by HBM memory, all on the same package.

It was the summer of 2015, a difficult period for AMD (there was talk of bankruptcy), but in which the company was laying the foundations for the revival that would come from 2017 onwards. Today AMD fortunately operates on other bases and with quite different perspectives, and as is known it has managed to reach and exceed the 32 core target, but only on "traditional" chips. What happened to the APU project then? Was deleted? It seems like no, is only proceeding with the headlights off.

The original design of Exascale Heterogeneous Processor (EHP)

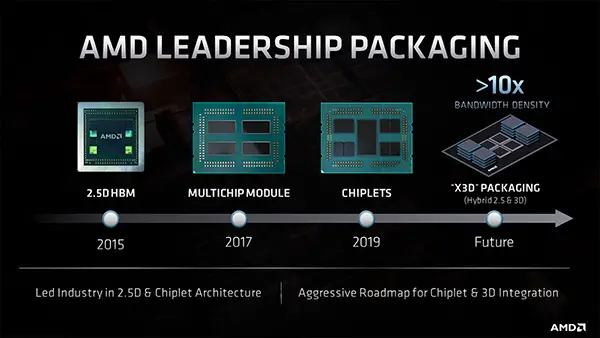

The Underfox user on Twitter has discovered several patents which shows that the EHP project is still alive and well, and that AMD is just waiting for the right technology to make its idea come true. That technology should be X3D, whose arrival was anticipated during the last Financial Analyst Day in early March.

X3D represents a hybrid 3D package that provides vertical and horizontal connections between the chips mounted on the package. Obviously it is only a piece of a more complex framework that would provide a MCM (multi-chip module) project for CPU and GPU, with dynamic and consistent memory management.

Click to enlarge

In fact, in a 2017 presentation, there was talk of Exascale Node Architecture (ENA), of which EHP was only a part. "ENA consists of an Exascale Heterogeneous Processor (EHP) coupled with an advanced memory system. EHP is made up of high performance computing units (CPU + GPU), HBM 3D memory on the same package and an aggressive use of die stacking and chiplet to meet the requirements of exascale computing in a balanced way ".

To all this were added advanced energy connection and management techniques, as well as full support from the frameworks based on the Heterogeneous System Architecture (HSA) and Radeon Open Compute (ROCm) ecosystems.

At the time, AMD thought of eight chiplets with four Zen cores each for the CPU, with optional Simultaneous Multi-Threading (SMT). The GPU instead would have counted on eight chiplets, each with 32 CU. Each graphics chiplet would have guaranteed a power of 2 TFLOPs with FP64 calculations (double precision), for a total total (CPU + GPU) of 16 TFLOPs. "With a system equipped with 100,000 knots it would be 1.6 power exaflops"said AMD.

Obviously it is obvious to say that the APU, if and when it arrives, will be based on the latest generation Zen architecture and a version of the CDNA architecture, as well as the latest technology available in terms of HBM memory.

Recall that AMD has signed contracts for two exascale HPCs called Frontier and El Capitan, but at the moment it does not seem to involve the use of an APU of this kind, but rather EPYC processors and Radeon Instinct accelerators.