The increase in power that processors will undergo in the coming years will only be comparable to what they offered at the time at the beginning of this century. And it is accelerating towards much more advanced lithographic processes that are going to bring, apart from the improvements in the architecture itself, a fairly significant increase in the number of cores.

Therefore, the amount of information to handle and work will be very high, so the RAM must match, as well as the BMI. In the latter we do not know how both Intel and AMD will manage it and above all at what rate, but what we can be sure of is what SK Hynix has prepared for this new revolution.

More speed, higher capacity and lower voltage: this is how Hynix sees DDR5

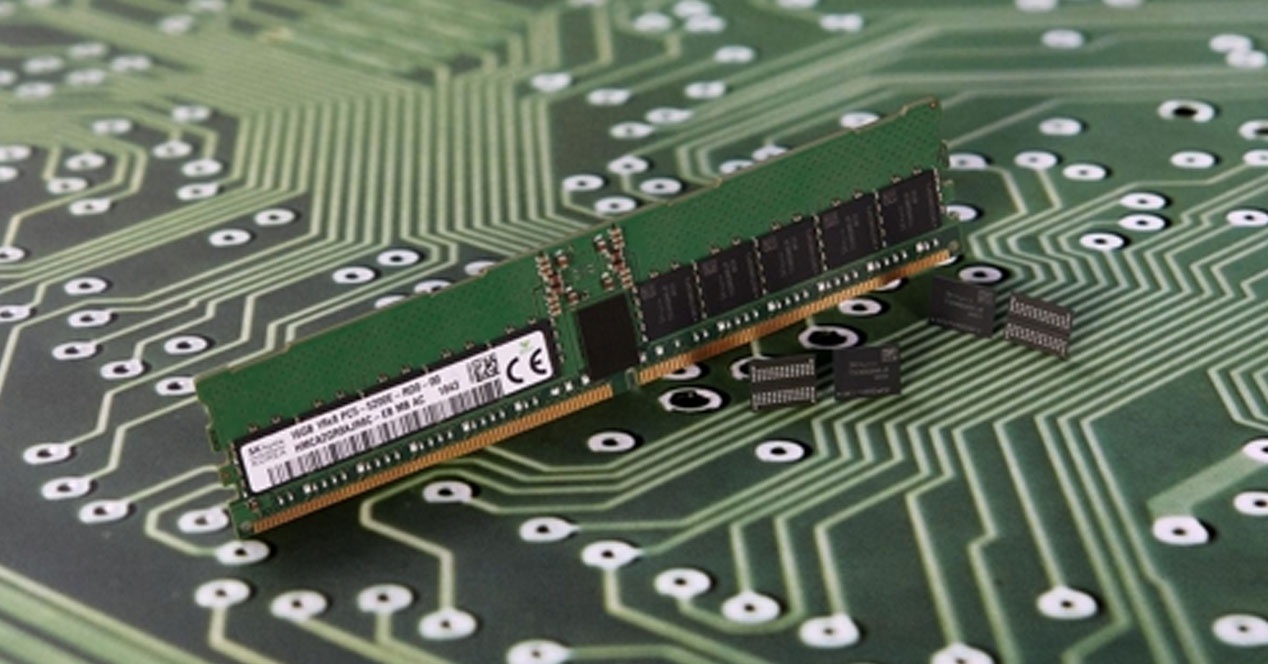

In addition to the aforementioned improvements, SK Hynix will introduce, according to the JEDEC standard, a new improvement that will ensure the data: ECC. As they have commented, they have been working on their DDR5-6400 modules, which would reach the market in a simple configuration of 16 GB.

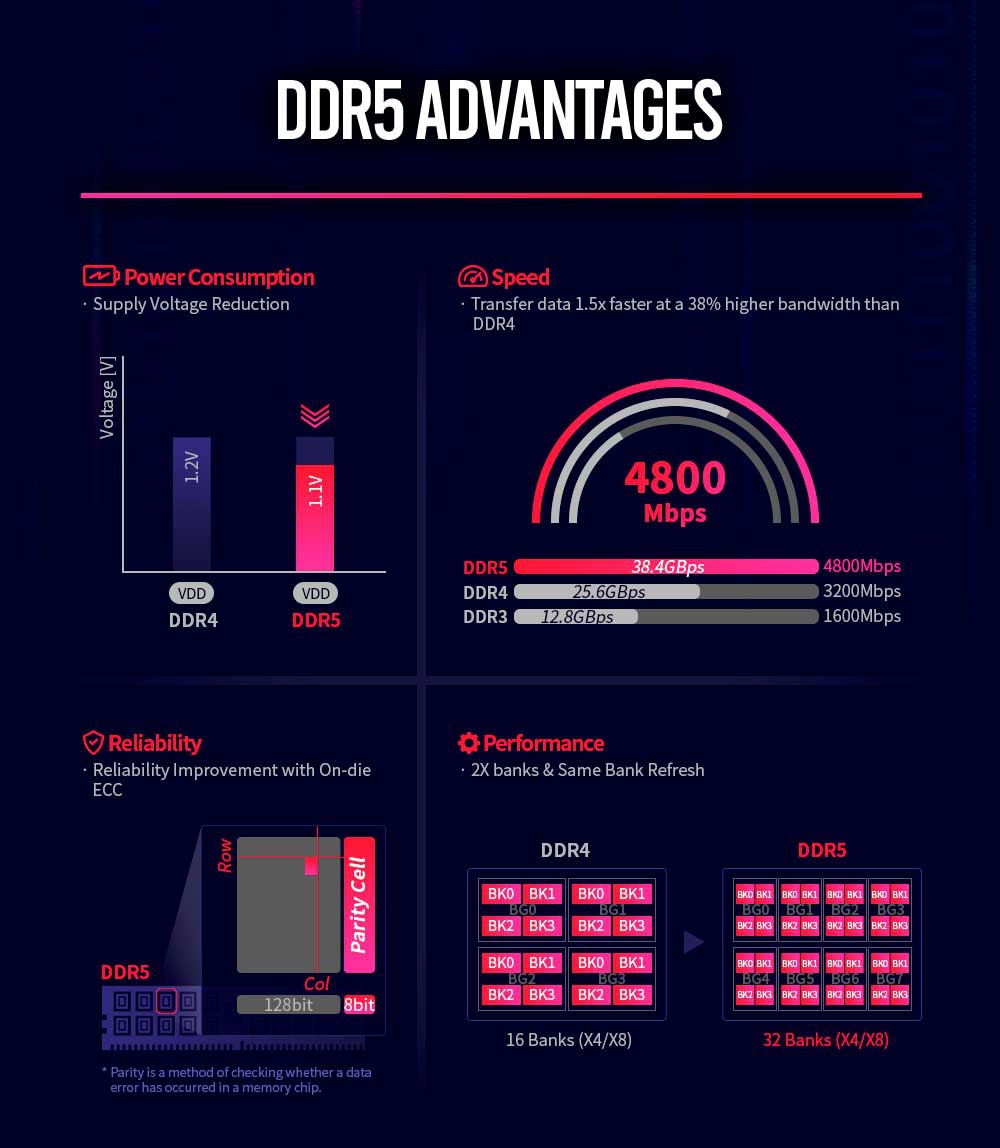

The difference with the current modules in terms of performance is not only about the pure speed difference that they are going to acquire, but also the number of banks that the new DDR5 is capable of accommodating compared to the current DDR4.

This also has another effect that DDR4 cannot achieve, and it is the update of the bank when it is being used, that is, until now the system did not allow using other banks while one was being updated, which with DDR5 it will be possible and with This improves the availability of memory access.

More efficient, safer and cheaper?

As we have said, SK Hynix sees the DDR5 with a quite wide perspective, and that is that it will arrive with its new 10 nm lithographic process in the second generation, which means a further reduction in manufacturing costs. In addition, to this we must add two crucial and inherent advantages to DDR5's own architecture as memory: ECC and ECS.

Error correction and error checking and elimination will reach this type of memory and each array, so error and defect detection is expected to be crucial to lower final costs before each module leaves the factory, which would greatly reduce the number of faulty modules and therefore RMAs.