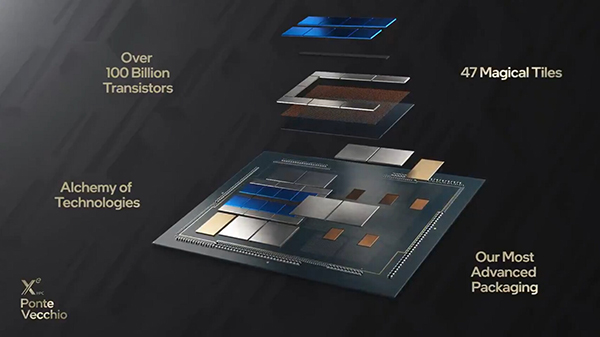

Intel Ponte Vecchio (Xe HPC) has 47 tiles and more than 100 billion transistors

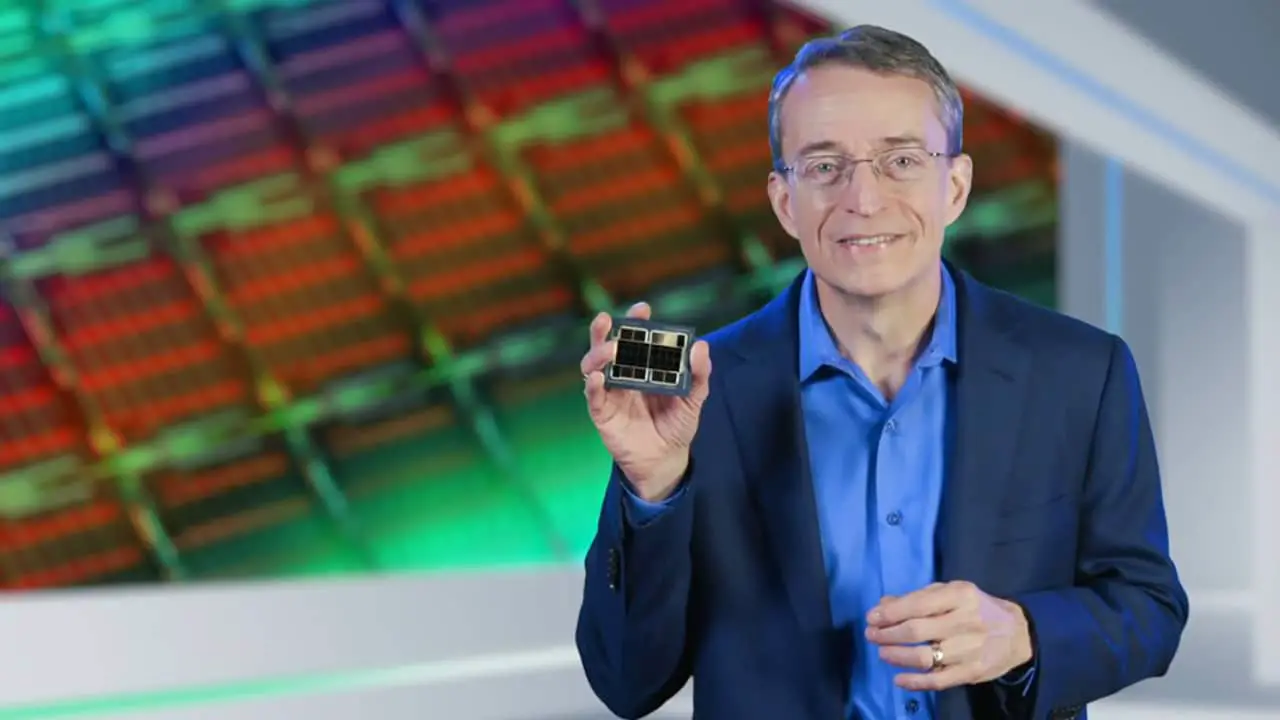

At the Intel Unleashed event there was no talk of gaming video cards as we hoped, but that does not mean that there was no protagonist GPU, albeit briefly: CEO Pat Gelsinger showed Old Bridge, an XPU (as the company defines it) based on architettura Vehicle HPC able to achieve calculation performance higher than the petaflop, the whole in the palm of your hand. Think that such computing power, 30 years ago, required a very large room with a series of servers.

Ponte Vecchio is a project dedicated to supercomputer exascale (1 exaflop and beyond), starting with Aurora – installed at the Argonne National Laboratory – designed for loads of artificial intelligence and usable by developers through oneAPI, the unified API on which the company has been working for some time to allow programming on all its architectures, from CPUs to GPUs to get to more specialized projects, in a simple way. Ponte Vecchio represents the mother of all Raja Koduri projects, chief architect of the architecture, software and graphics division at Intel.

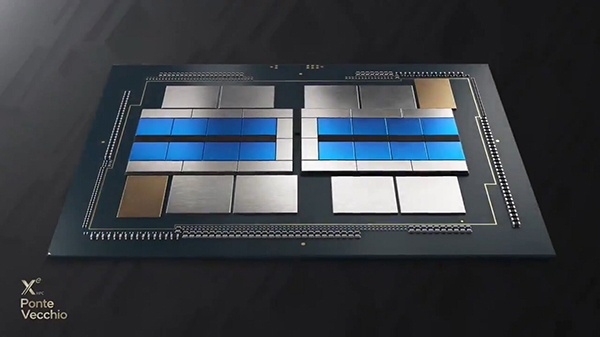

Being a product based on multiple tiles (as many as 47) joined together through packaging and interconnection technologies such as Foveros and EMIB, not all the elements of Ponte Vecchio are produced internally. A slide from last August illustrates the breakdown, with some elements made in Intel factories such as Rambo Cache and others that will be made by other companies such as TSMC and then assembled by Intel:

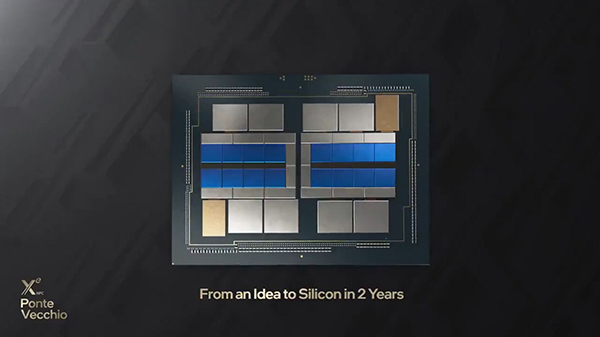

In a video, which you find below, Intel states that Ponte Vecchio is a project conceived and built in about 2 years, a decidedly short timeframe if we think of the high rate of innovation and complexity. Ponte Vecchio represents, if you want, the best spot of Intel’s capabilities in terms of design and execution, and this could be really useful in finding new customers for its production lines.

This 47-tile super project has over 100 billion transistors and will be used in supercomputers alongside the Xeon CPUs codenamed Sapphire Rapids. Ponte Vecchio will probably enter a collision course with the Nvidia and AMD accelerators of 2022, on the one hand the rumored Hopper, on the other a project based on CDNA 2 architecture. chiplet.