Intel: after the Ponte Vecchio accelerator it’s up to Rialto Bridge

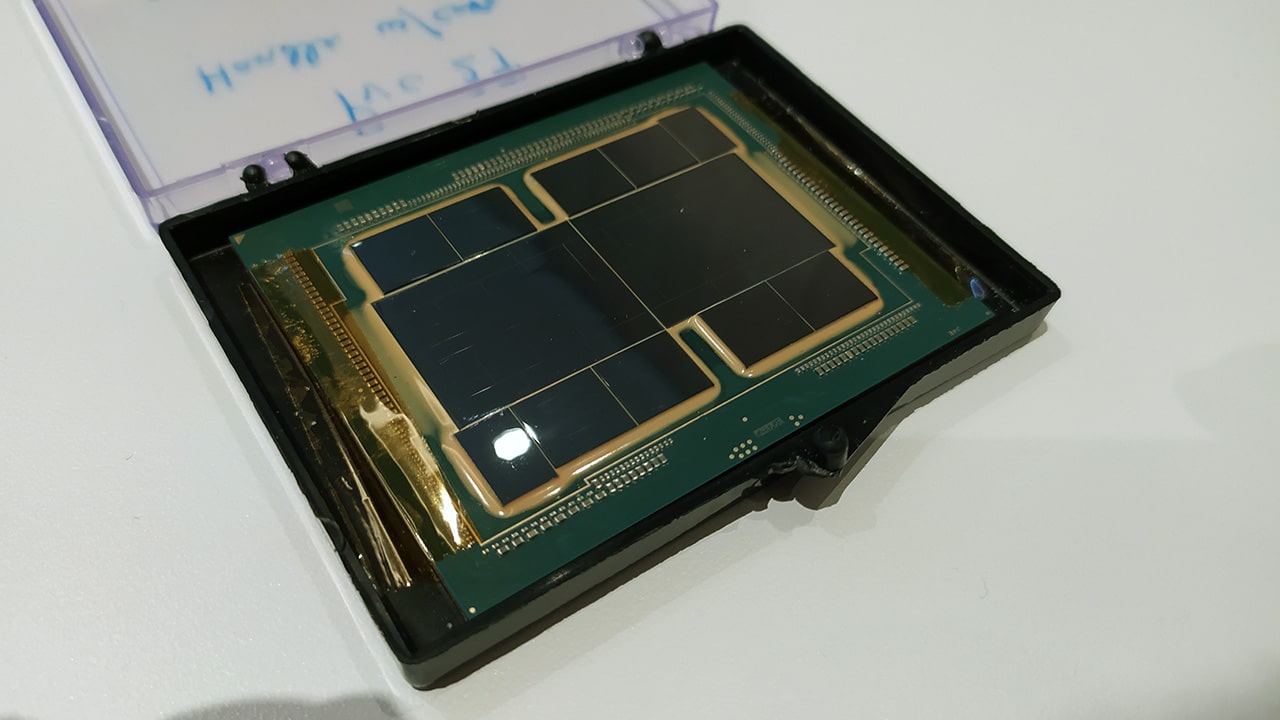

Non solo Sapphire Rapids, Intel now ready to introduce the other element of its renewed strategy in the supercomputer sector, the accelerator Old Bridge based on Xe HPC architecture. We have talked about it several times in the past, but at the German event Intel not only allowed us to photograph it closelyboth the single chip and the accelerator in OAM format, but he also told us about what to come next.

Ponte Vecchio is a truly complex project that counts over 100 billion transistors and a total of 47 tiles joined together through packaging and interconnection technologies such as Foveros and EMIB. Not all elements of Ponte Vecchio are produced internally by Intel, some are made by TSMC. In addition, 128 GB of HBM2E memory is on board.

The accelerator, together with the Sapphire Rapids CPUs, will be the heart of the Aurora supercomputer that aspires to surpass a computing power of 2 exaflops, leaving behind the Frontier, the new fastest system in the world.

The company also confirmed to us that roughly in the middle of 2023 we will see Rialto Bridge, the successor of Ponte Vecchio. Jeff McVeigh, VP and GM of the Super Compute Group, explained to us that Rialto Bridge represents a “Tick“in Intel’s” Tick-Tock “strategy: in practice, the company will not propose a new architecture, but by practicing various efficiencies – including the use of better manufacturing processes will be able to guarantee more performance and bandwidth.

Among the steps forward we find the increase of the Xe cores, from a maximum of 128 up to 160, so is the transition to a second generation OAM format. Furthermore, a rationalization of the project, with the passage to fewer tiles, cannot be ruled out. McVeigh, in the chat with the European press, did not hide the fact that complexity is shifting from the chips to the package.