PCI Express 6.0 Completed: Double the bandwidth compared to PCI Express 5.0

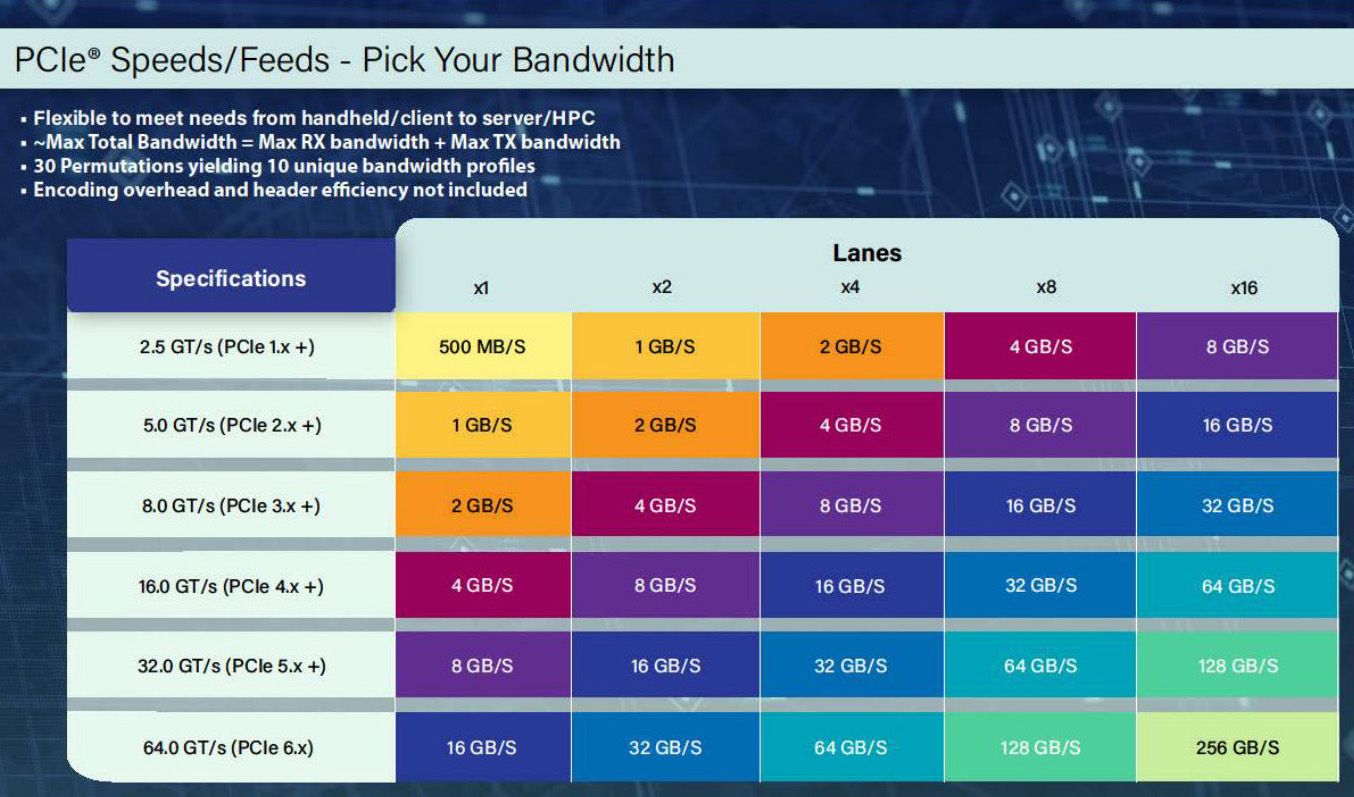

The PCI Express 6.0 it is technically early. The PCI Special Interest Group (PCI-SIG) has released version 1.0 of the specification to its members. Also this version of the interface doubles the data rate for each line, bringing it to 16 GB / s bidirectional for single line (x1) and to 256 GB / s bidirectional in the maximum expression composed of 16 lines (x16).

Completed the development, the consortium believes that the first compatible products (in the server sector) will arrive on the market within 12-18 months. As with previous versions, 6.0 will also guarantee the backward compatibility with the generations that preceded it and this therefore means that the connector will not change.

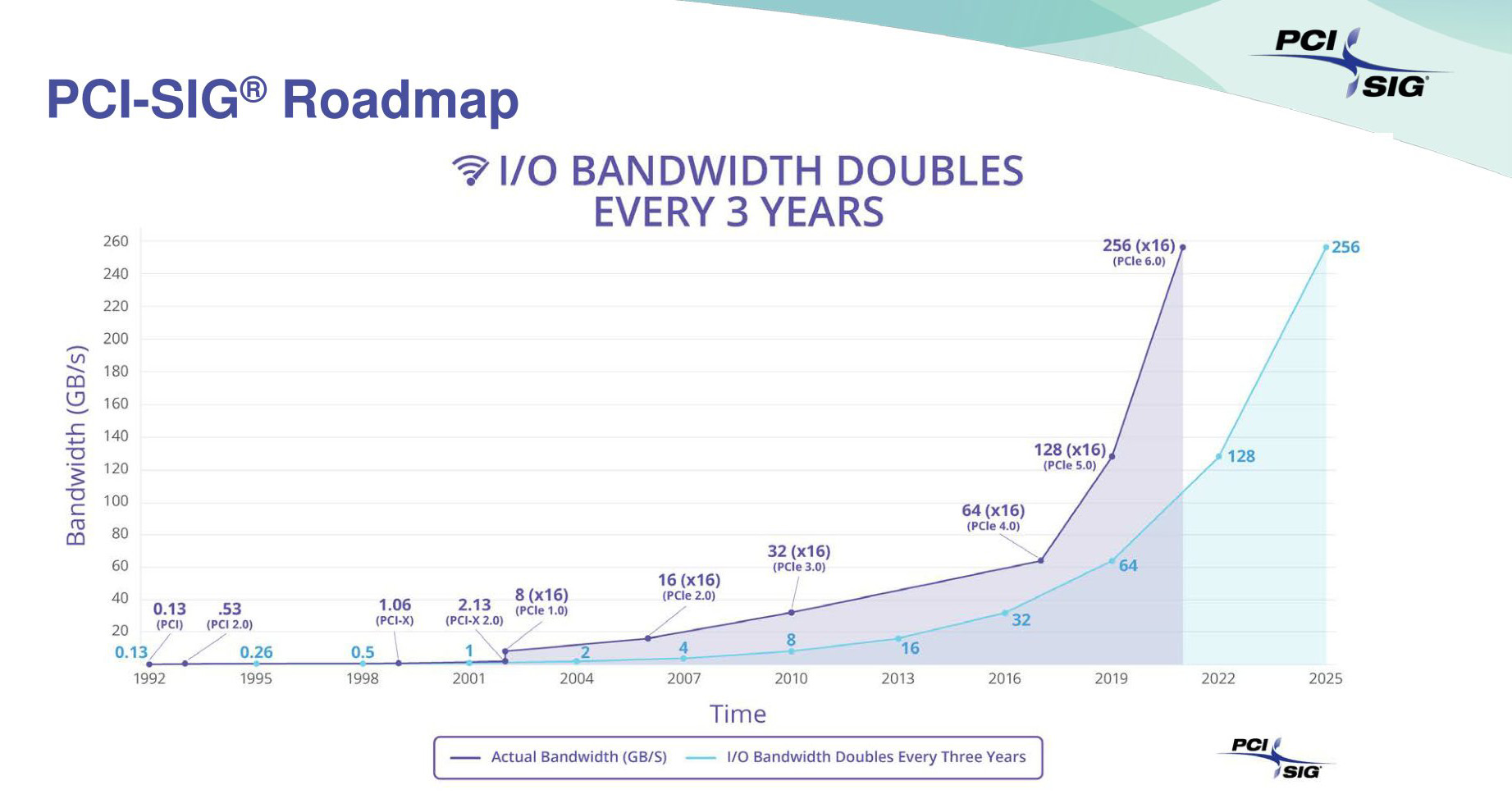

Development of PCI Express 6.0 started in 2019, so the consortium has kept their promise to finalize a new version of the standard every three years or so to satisfy the hi-tech industry’s thirst for bandwidth, particularly that of the industry. server.

As always, the new version it will also arrive in the consumer sector, although today it is not known when: Intel and AMD are currently focused on PCI Express 5.0, both in the server and client fields, for the moment they have not talked about PCI Express 6.0, but their adoption will be the driving force.

In order to double the bandwidth, the PCI-SIG has adopted a new signaling technology, moving from the previous Non-Return-to-Zero (NRZ) to the new Pulse-Amplitude Modulation 4 (PAM4). PAM4, that is the modulation of the pulse width at four levels, is a solution chosen by Micron also for the GDDR6X memories of the GeForce RTX 3000 cards.

While NRZ is based on traditional two-level coding (0 or 1), PAM4 adopts four levels of two-bit signals (00, 01, 10, 11) to carry double the data without having to double the transmission bandwidth (and consequently the operating frequency). For this to be possible, the PCI-SIG had to implement for the first time a mechanism called Forward Error Correction (FEC) to ensure signal integrity, as well as another solution called Cyclic Redundancy Check (CRC).

A further novelty in addition to PAM4 and FEC takes the name of FLow control unIT (FLIT), a logic-level coding method for splitting data into fixed-size packets functional to the implementation of FEC, and other error correction methods that require packets of a certain size. According to the PCI-SIG, FLIT is one of the most important parts of the specification, as it is the key to enabling low-latency operation of PCIe with FEC, as well as ensuring low overhead.